# CS:4980 Foundations of Embedded Systems

## Synchronous Model Part II

Copyright 2014-20, Rajeev Alur and Cesare Tinelli.

Created by Cesare Tinelli at the University of Iowa from notes originally developed by Rajeev Alur at the University of Pennsylvania. These notes are copyrighted materials and may not be used in other course settings outside of the University of Iowa in their current form or modified form without the express written permission of one of the copyright holders. During this course, students are prohibited from selling notes to or being paid for taking notes by any person or commercial firm without the express written permission of one of the copyright holders.

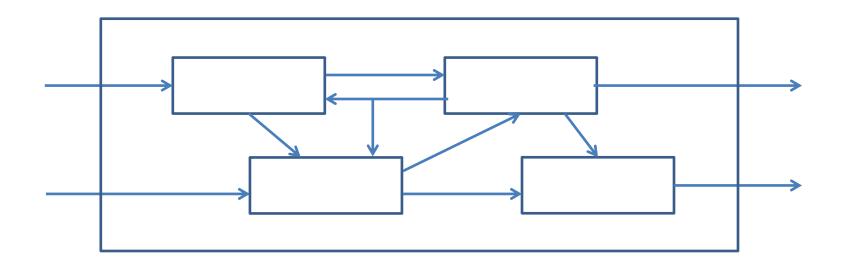

#### **Block Diagrams**

Structured modeling

- How do we build complex models from simpler ones?

- What are basic operations on components?

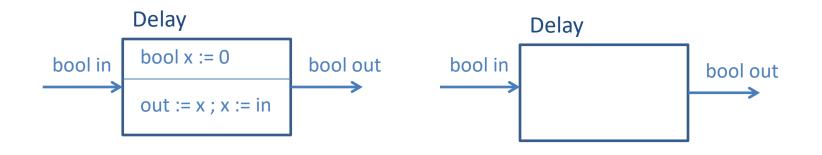

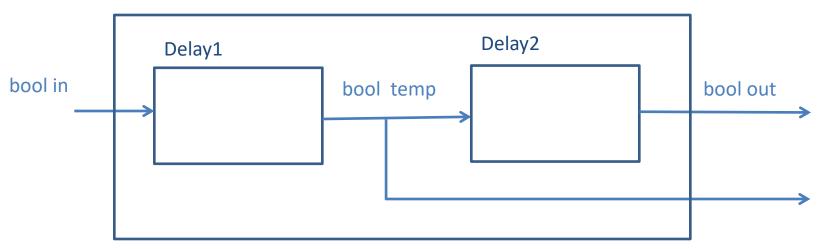

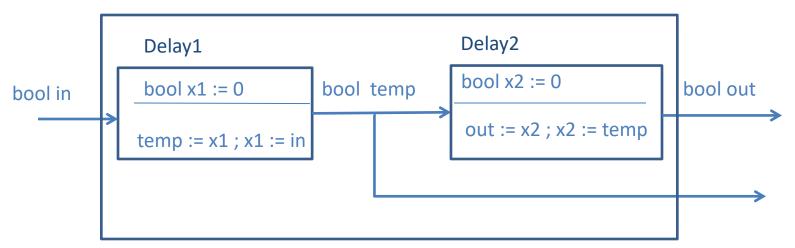

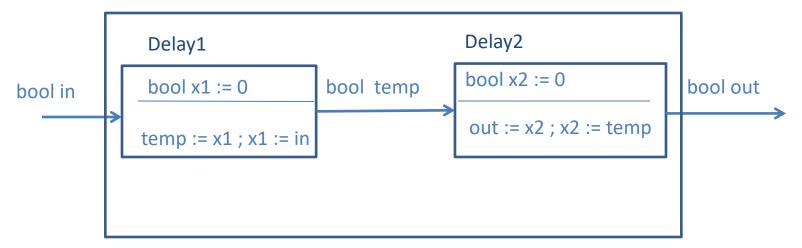

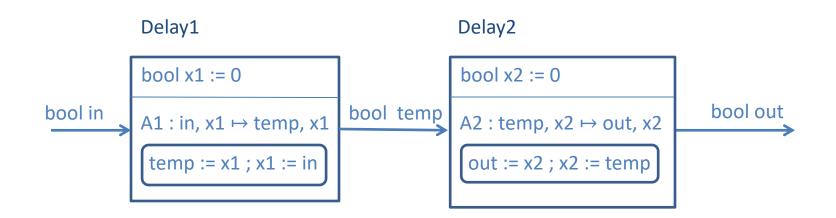

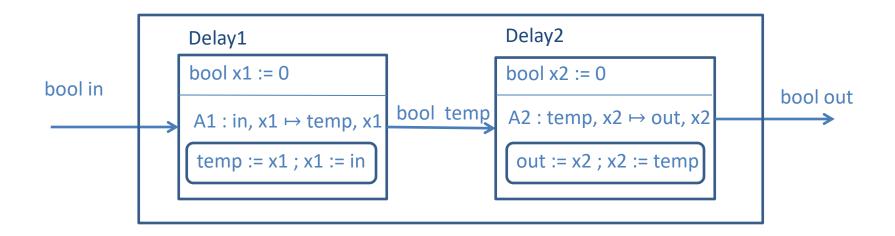

### DoubleDelay

Design a component with

- Input: bool in

- Output: bool out

- Output in round n should equal input in round n-2

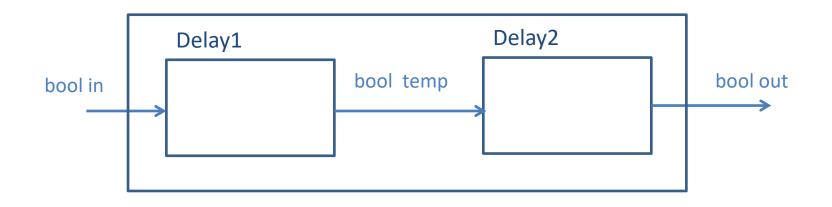

### DoubleDelay

- Instantiation: Create two instances of Delay

- Output of Delay1 = Input of Delay2 = Variable temp

- Parallel composition: Concurrent execution of Delay1 and Delay2

- **Encapsulation/Hiding:** Hide variable temp

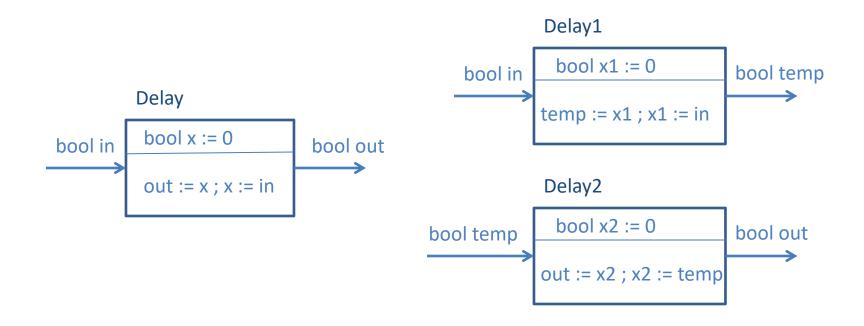

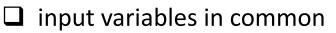

### Instantiation / Renaming

$\Box \text{ Delay1} = \text{Delay[out} \mapsto \text{temp]}$

- Explicit renaming of input/output variables

- Implicit renaming of state variables

- Components (I, O, S, Init, React) of Delay1 derived from Delay

- $\Box \text{ Delay2} = \text{Delay[in} \mapsto \text{temp]}$

### Parallel Composition (or Product)

#### DoubleDelay

#### DoubleDelay = Delay1 || Delay2

- Execute both concurrently

- □ When can two components be composed?

- □ How to define parallel composition precisely?

- Input/output/state variables, initialization, and reaction description of composite defined in terms of components

- Can be viewed as an algorithm for compilation

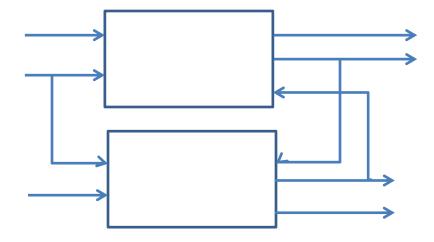

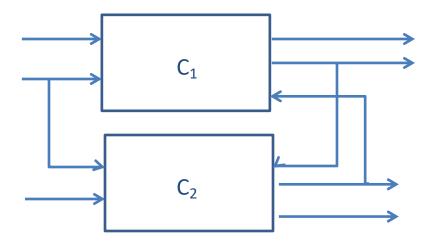

### Compatibility of Components C1 and C2

#### Allowed:

output variable of one is input variable of the other

#### **Disallowed:**

- output variables in common

- a unique component must be responsible for values of any given variable

state variables in common

but state variables can be implicitly renamed to avoid conflicts

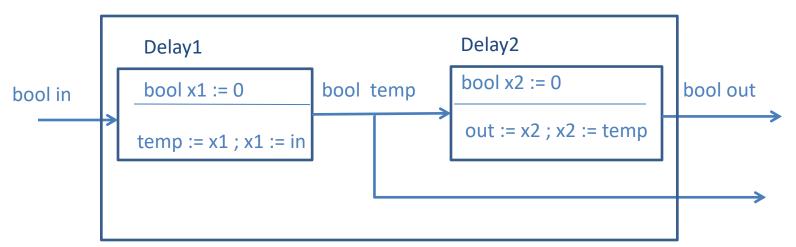

#### **Outputs of Product**

Delay1 || Delay2

- The output variables of Delay1 || Delay2 are {temp, out}

Note: by default, every output is available to outside world

- □ If C1 has output vars O1 and C2 has output vars O2 then the product C1 || C2 has output vars O1 ∪ O2

### **Inputs of Product**

Delay1 || Delay2

The input variables of Delay1 || Delay2 are {in}

- Even though temp is input of Delay2, it is not an input of product

- □ If C1 has input vars I1 and C2 has input vars I2 then C1 || C2 has input vars  $(|1 \cup |2) \setminus (01 \cup 02)$

- A variable is an input of the product iff it is an input of one of the components, and not an output of the other

#### **States of Product**

Delay1 || Delay2

□ The state variables of Delay1 || Delay2 are {x1, x2}

- □ If  $C_1$  has state vars  $S_1$  and  $C_2$  has state vars  $S_2$  then  $C_1 || C_2$  has state vars  $S_1 \cup S_2$  (recall that  $S_1 \cap S_2 = \emptyset$ )

- A state of the product is a pair (s<sub>1</sub>, s<sub>2</sub>), where s<sub>1</sub> is a state of C<sub>1</sub> and s<sub>2</sub> is a state of C<sub>2</sub>

- If  $C_1$  has  $n_1$  states and  $C_2$  has  $n_2$  states then  $C_1 \mid \mid C_2$  has  $n_1 \cdot n_2$  states

#### **Initial States of Product**

Delay1 || Delay2

□ The initialization code Init for Delay1 || Delay2 is x1 := 0 ; x2 := 0

- Initial states are { (0,0) }

- □ If C<sub>1</sub> has initialization Init<sub>1</sub> and C<sub>2</sub> has initialization Init<sub>2</sub> then C<sub>1</sub> || C<sub>2</sub> has initialization Init<sub>1</sub> ; Init<sub>2</sub> (or, equivalently, Init<sub>2</sub> ; Init<sub>1</sub>)

- Order does not matter

[Init] is the Cartesian product  $[Init]_1 \times [Init_2]$

#### **Reactions of Product**

Delay1 || Delay2

Execution of Delay1 || Delay2 within a round:

- environment provides input value for variable in

- execute code temp := x1 ; x1 := in of Delay1

- execute code out := x2 ; x2 := temp of Delay2

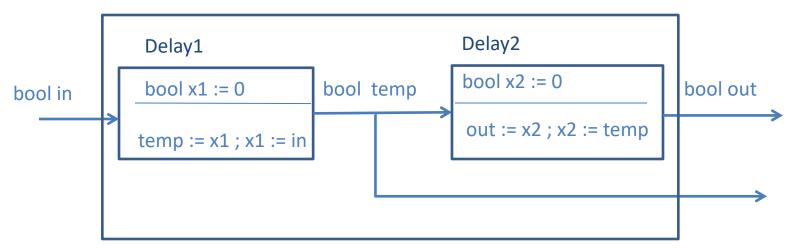

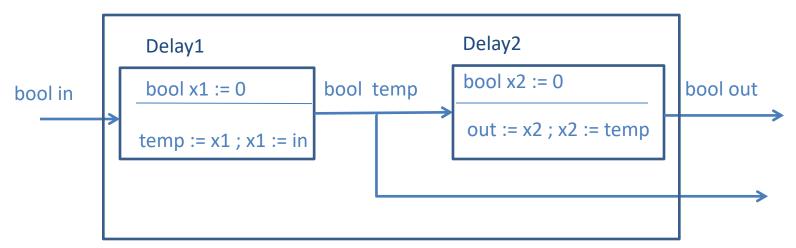

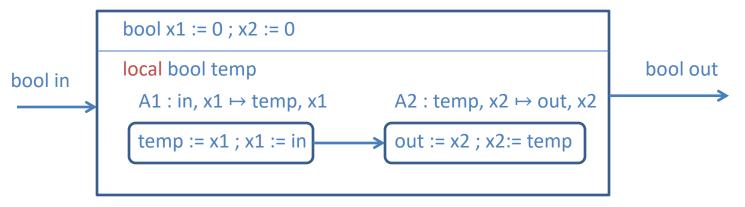

### **Final Composition**

#### $(Delay[out \mapsto temp] \mid \mid Delay[in \mapsto temp]) \setminus temp$

- Instantiation: Delay[out → temp] and Delay[in → temp]

- Parallel composition: Delay[out → temp] || Delay[in → temp]

- Output hiding: (Delay[out → temp] || Delay[in → temp]) \ temp

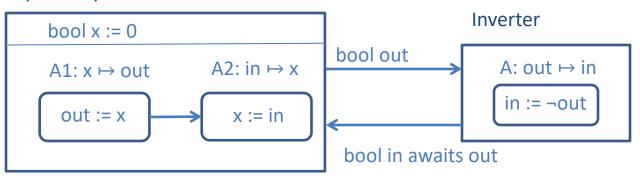

#### **Feedback Composition**

#### When

- some output of C<sub>1</sub> is an input of C<sub>2</sub>, and

- some output of C<sub>2</sub> is an input of C<sub>1</sub>,

how do we order the executions of reaction React<sub>1</sub> and React<sub>2</sub>?

□ Should such composition be allowed at all?

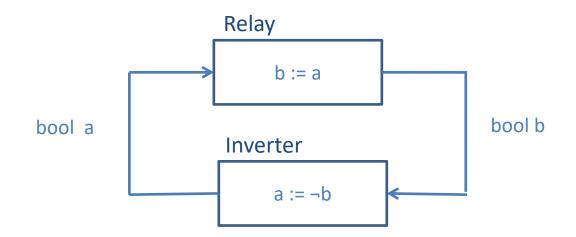

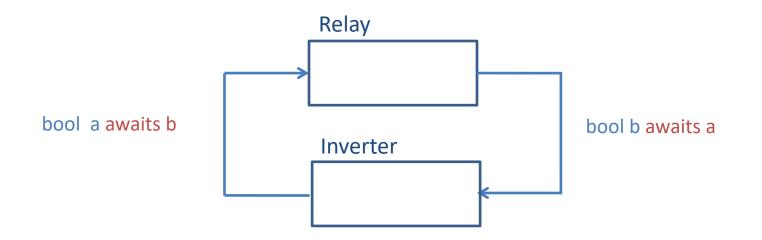

#### **Feedback Composition**

For Relay:its output b awaits its input aFor Inverter:its output a awaits its input b

- □ In product, we cannot order the execution of the two

- □ In the presence of such cyclic dependency, composition is disallowed

- □ Intuition: combinational cycles should be avoided

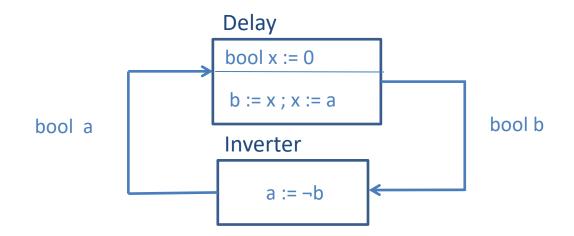

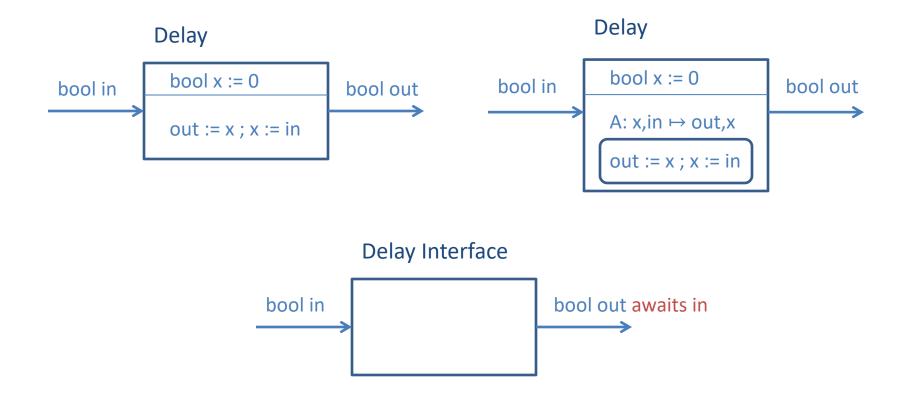

#### **Feedback Composition**

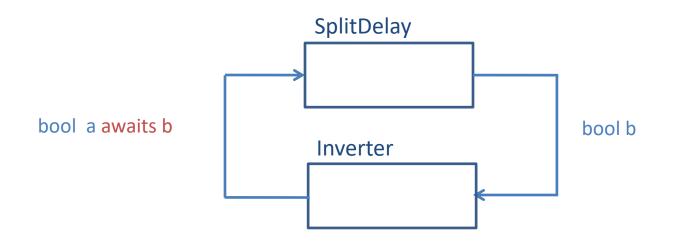

For Delay, it is possible to produce output without waiting for its input by executing the assignment b := x

- **Q** Reaction code for Delay || Inverter could be b := x;  $a := \neg b$ ; x := a

- □ Goal: Refine specification of reaction description so that await dependencies among output-input variables are easy to detect

- Ordering of code-blocks during composition should be easy

#### Interfaces

Interface = (input variables, output variables, await dependencies)

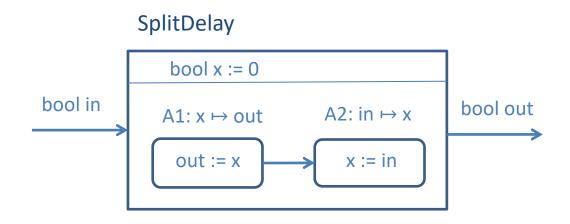

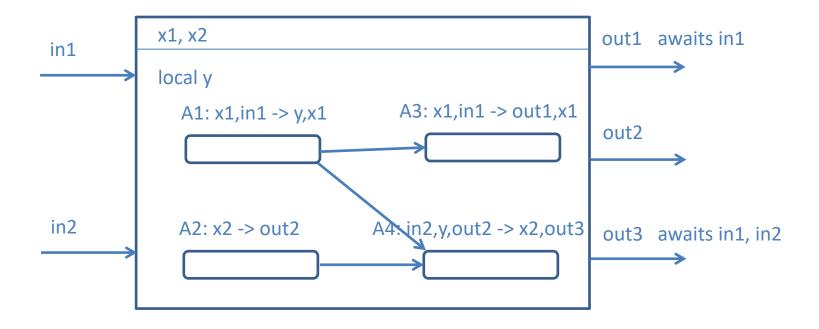

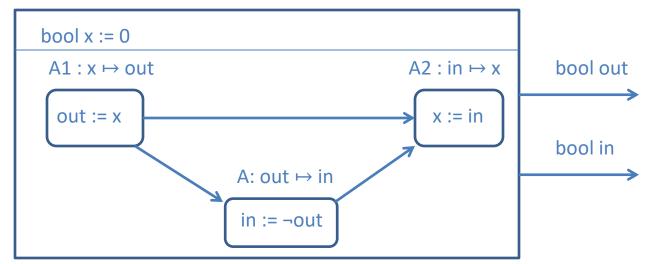

### Interface: SplitDelay

Decomposing the reaction into tasks eliminates in this case the await dependency between out and in

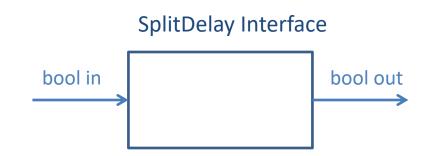

#### Example Interface

#### **Example Interface**

#### **Back to Parallel Composition**

Relay and Inverter are not compatible since there is a cycle in their combined await dependencies

#### **Composing SplitDelay and Inverter**

SplitDelay and Inverter are compatible since there is no cycle in their combined await dependencies

**Note:** Based on their interfaces, Delay and Inverter are not compatible

#### **Component Compatibility Definition**

#### Given components :

- $C_1$  with input vars  $I_1$ , output vars  $O_1$ , and awaits-dep. relation  $>_1$

- $C_2$  with input vars  $I_2$ , output vars  $O_2$ , and awaits-dep. relation  $>_2$

- **C**<sub>1</sub> and C<sub>2</sub> are *compatible* if

- they have no common outputs: sets O<sub>1</sub> and O<sub>2</sub> are disjoint

- the relation  $>_1 \cup >_2$  of combined await-dependencies is acyclic

Parallel Composition is allowed only for compatible components

#### **Defining the Product**

Delay1 || Delay2

#### **Composing SplitDelay and Inverter**

SplitDelay

SplitDelay || Inverter

#### **Parallel Composition Definition**

Given compatible components

- $C_1 = (I_1, O_1, S_1, Init_1, React_1)$  and

- C<sub>2</sub> = (I<sub>2</sub>, O<sub>2</sub>, S<sub>2</sub>, Init<sub>2</sub>, React<sub>2</sub>),

what's the reaction of product  $C = C_1 || C_2$ ?

Suppose React<sub>1</sub> and React<sub>2</sub> are specified using resp.

- Iocal vars L<sub>1</sub>, set of tasks P<sub>1</sub>, and precedence <<sub>1</sub>, and

- Iocal vars L<sub>1</sub>, set of tasks P<sub>2</sub>, and precedence <<sub>2</sub>

- Reaction description for product C has

- local variables  $L_1 \cup L_2$

- set of tasks  $P_1 \cup P_2$

- precedence edges <<sub>1</sub> ∪ <<sub>2</sub> ∪ {edges between tasks A<sub>1</sub> and A<sub>2</sub> of different components if A<sub>2</sub> reads a var written by A<sub>1</sub>}

#### **Parallel Composition Definition**

Why is the parallel composition operation well-defined?

- Can the new edges make task graph of the product cyclic?

- Recall: Await-dependencies among I/O variables of compatible components must be acyclic

- Proposition 2.1: Awaits compatibility implies acyclicity of product task graph

- Bottom line: Interfaces capture enough information to define parallel composition in a consistent manner

- Aside: It is possible to define more flexible (but more complex) notions of awaits dependency

#### **Properties of Parallel Composition**

- **Commutative:**  $C_1 || C_2 = C_2 || C_1$  (when  $C_1, C_2$  are compatible)

- Associative:  $(C_1 | | C_2) | | C_3 = C_1 | | (C_2 | | C_3)$

- If compatibility check fails in one case, will also fail in others

- **Bottom line:** order of composition does not matter

- If  $C_1$  has  $n_1$  states and  $C_2$  has  $n_2$  states then  $C_1 || C_2$  has  $n_1 \cdot n_2$  states

- If both  $C_1$  and  $C_2$  are deterministic, so is  $C_1 || C_2$

- □ If both C<sub>1</sub> and C<sub>2</sub> are event-triggered, is C<sub>1</sub> || C<sub>2</sub> guaranteed to be event-triggered?

### **Output Hiding**

Let C be a component and y one of its output vars

- The result of hiding y in C, written as C \ y, is a component identical to C except that y is no longer an output variable but a local variable

- This is useful for limiting the scope or a component (encapsulation)

#### DoubleDelay

(Delay1 || Delay2) \ temp

### Credits

Notes based on Chapter 2 of

**Principles of Cyber-Physical Systems**

by Rajeev Alur MIT Press, 2015