# Logic Design (continued)

#### XOR Revisited

XOR is also called modulo-2 addition.

| Α | В | С | <u> </u> |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 0        |

| 1 | 1 | 0 | 0        |

| 1 | 1 | 1 | 1        |

$A \oplus B = 1$  only when there are an odd number of 1's in (A,B). The same is true for  $A \oplus B \oplus C$  also.

$$1 \oplus A = \overline{A}$$

$$0 \oplus A = A$$

Why?

## Logic Design Examples

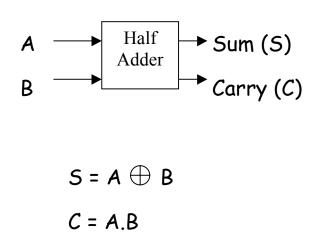

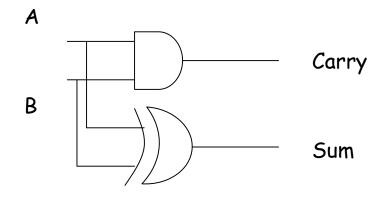

### <u>Half Adder</u>

| Α | В | 5 | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

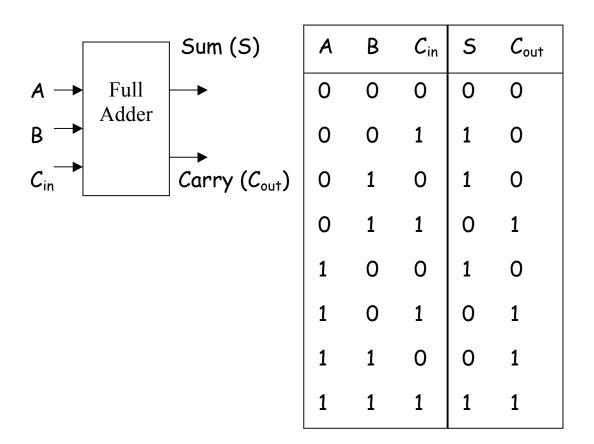

#### Full Adder

$S = A \oplus B \oplus C_{in}$  $C_{out} = A.B + B.C_{in} + A.C_{in}$

Design a full adder using two half-adders (and a few gates if necessary) Can you design a 1-bit subtracter?

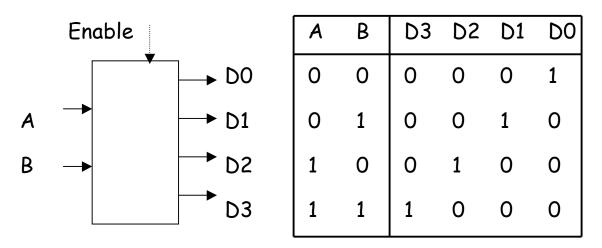

#### Decoders

A typical decoder has n inputs and 2<sup>n</sup> outputs.

A 2-to-4 decoder and its truth table

D3 = A.B D2 = A.B D1 = A.B D0 = A.B

Draw the circuit of this decoder.

The decoder works per specs when (Enable = 1). When Enable = 0,

all the outputs are 0.

Exercise. Design a 3-to-8 decoder.Question. Where are decoders used?Can you design a 2-4 decoder using 1-2 decoders?

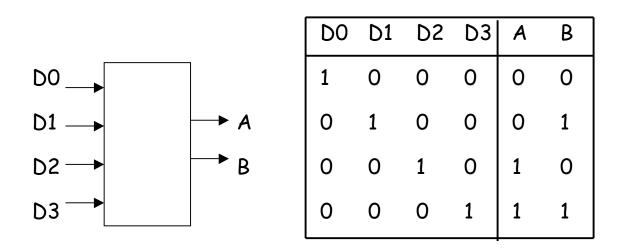

### Encoders

A typical encoder has 2<sup>n</sup> inputs and n outputs.

A 4-to-2 encoder and its truth table

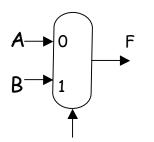

#### <u>Multiplexor</u>

It is a many-to-one switch, also called a selector.

S = 0, F = A S = 1, F = B

Control S

Specifications of the mux

A 2-to-1 mux

Exercise. Design a 4-to-1 multiplexor using two 2-to-1 multiplexors.

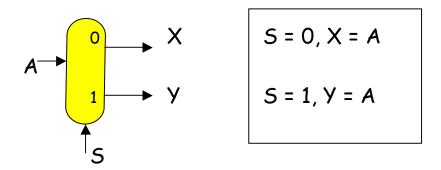

#### **Demultiplexors**

A demux is a one-to-many switch.

A 1-to-2 demux, and its specification.

**Exercise**. Design a 1-4 demux using 1-2 demux.