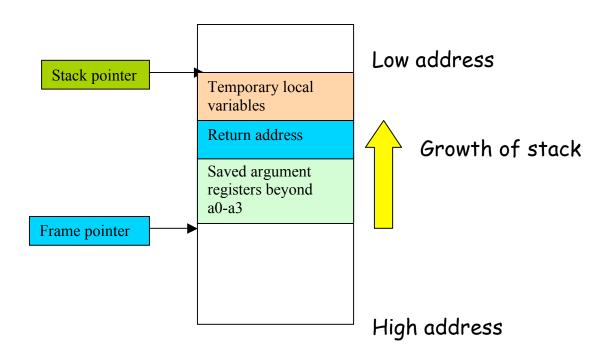

# Run time environment of a MIPS program

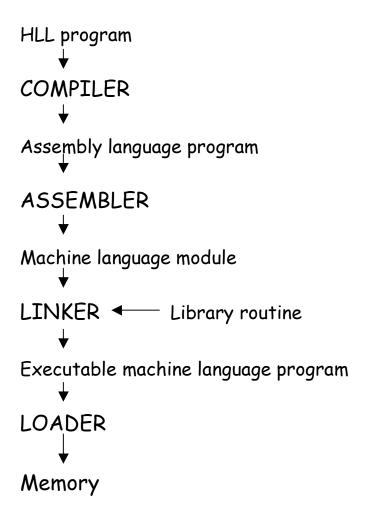

# A translation hierarchy

# What are Assembler directives?

Instructions that are not executed, but they tell the assembler about how to interpret something. Here are some examples:

```

. text

{Program instructions here}

. data

{Data begins here}

. byte 84, 104, 101

. asciiz "The quick brown fox"

. float f1,..., fn

. word w1,.... wn

```

# How does an assembler work?

In a two-pass assembler

PASS 1: Symbol table generation

PASS 2: Code generation

The operation of a two-pass assembler has been briefly explained in the class on 2/9/10.

### Other architectures

Not all processors are like MIPS.

### Example. Accumulator-based machines

A single register, called the accumulator, stores the operand before the operation, and stores the result after the operation.

| Load  | X | # into acc from memory         |

|-------|---|--------------------------------|

| Add   | У | # add y from memory to the acc |

| Store | Z | # store acc to memory as z     |

Can we have an instruction

add

$$z, x, y$$

#  $z = x + y, (x, y, z \text{ in memory})$ ?

For some machines, YES, not in MIPS

#### Load-store machines

MIPS is a load-store architecture. Only load and store instructions access the memory, all other instructions use registers as operands. What is the motivation?

Register access is much faster than memory access, so the program will run faster.

#### Reduced Instruction Set Computers (RISC)

- The instruction set has only a small number of frequently used instructions. This lowers processor cost, without much impact on performance.

- All instructions have the same length.

- Load-store architecture

Non-RISC machines are called CISC

(Complex Instruction Set Computer). Example: Pentium

## Another classification

3-address add r1, r2, r3  $(r1 \leftarrow r2 + r3)$

2-address add r1, r2  $(r1 \leftarrow r1 + r2)$

1-address add r1 (to the accumulator)

O-address or stack machines (see below)

# Example of stack architecture

Push x

Push y

Push z

X

y z

х **у+**z

x \* (y+z)

Add

Multiply

Pop z

Computes z = x \* (y + z)

### Computer Arithmetic

How to represent negative integers? The most widely used convention is 2's complement representation.

Largest integer represented using n-bits is  $+2^{n-1}-1$ Smallest integer represented using n-bits is  $-2^{n-1}$

Review binary-to decimal and binary-to-hex conversions.

Review BCD (Binary Coded Decimal) and ASCII codes.

How to represent fractions?

### **Overflow**

$$+12 = 0,1100$$

$+12 = 0,1100$

$+2 = 0,0010$   $+7 = 0,0111$

add — add

$+14 = 0,1110$   $? = 1,0011$

Addition of a positive and a negative number does not lead to overflow. How to detect overflow?

The following sequence of MIPS instructions can detect overflow in signed addition of \$11 and \$12:

```

addu $t0, $t1, $t2 # add unsigned

xor $t3,$t1,$t2 # check if signs differ

slt $t3, $t3, $zero # $t3=1 if signs differ

bne $t3 $zero, no_overflow

xor $t3, $t0, $t1 # sum sign = operand sign?

slt $t3, $t3, $zero # if not, then $t3=1

bne $t3, $zero, overflow

no_overflow:

overflow:

<Do something to handle overflow>

```

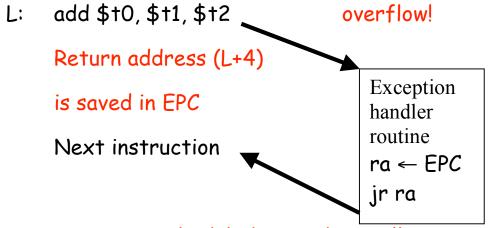

### The Basics of Exception Handling

MIPS uses two coprocessors: CO and C1 for additional help. CO primarily helps with exception handling, and C1 helps with floating point arithmetic.

#### **Interrupts**

Initiated outside the instruction stream

Arrive asynchronously (at no specific time),

Example:

- I/O device status change

- I/O device error condition

#### Traps

Occur due to something in instruction stream.

#### Examples:

- Unaligned address error

- Arithmetic overflow

- System call

MIPS coprocessor CO has a cause register (Register 13) that contains a 5-bit code to identify the cause of an exception

#### Cause register

| pending<br>interrupt | exception code |

|----------------------|----------------|

| 15-10                | bits 6-2       |

MIPS instructions that cause overflow (or some other violation) lead to an *exception*, which sets the exception code. It then switches to the kernel mode (designated by a bit in the status register of CO, register 12) and transfer control to a predefined address to invoke a routine (exception handler) for handling the exception.

Exceptions cause unscheduled procedure calls.

### More Programming Examples

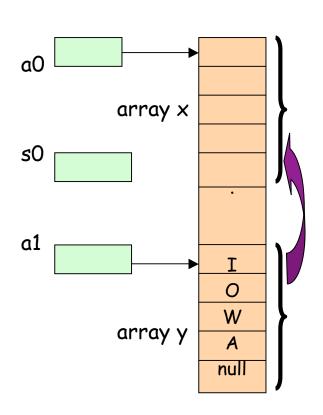

### Copying a string

Each char is represented by an ASCII byte. The string is terminated by a Null in ASCII). Reg s0 will hold the array index.

```

add $s0, $zero, $zero

#i = 0

L1:

add $t1, $a1, $s0

# address of y[i] in t1

/b $t2, 0($t1)

# + 2 = y[i]

Load

add $t3, $a0, $s0

# address of x[i] in t3

byte

sb $t2, 0($t3)

\# x[i] = y[i]

\# i = i+1

addi $s0, $s0, 1

bne $t2,$zero, L1

# if y[i] \neq 0 then go to L

```